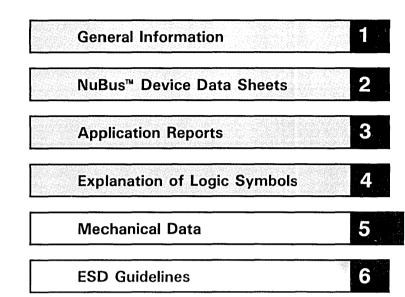

# **NuBus**<sup>™</sup> Interface Products

## NuBus<sup>™</sup> Interface Products Data Book

### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Texas Instruments products are not intended for use in life support appliances, devices or systems. Use of a TI product in such applications without the written consent of the appropriate TI officer is prohibited.

Copyright © 1990, Texas Instruments Incorporated

Printed in the U.S.A.

## INTRODUCTION

This Data Book presents technical information on the TI NuBus<sup>\*\*</sup> support product line. Specifications and operational information is included for the following high-performance Advanced-CMOS devices:

- 1. SN74ACT2440 NuBus™ Interface Controller

- 2. SN74ACT2441 MCP<sup>†</sup> NuBus™ Interface Controller

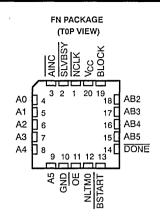

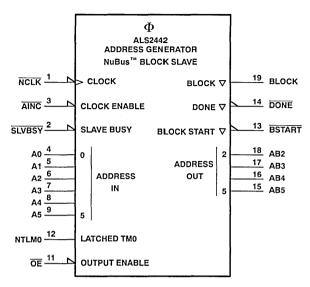

- 3. SN74ALS2442 -- NuBus™ Block Slave Address Generator

- 4. SN74BCT2420 -- NuBus™ Address/Data Tranceiver and Registers

- 5. SN74BCT2423/24 16-Bit Latched Multiplexer/Demultiplexer Bus Transceivers

- 6. SN74BCT2425 MCP<sup>†</sup> NuBus<sup>™</sup> Address/Data Tranceivers and Registers.

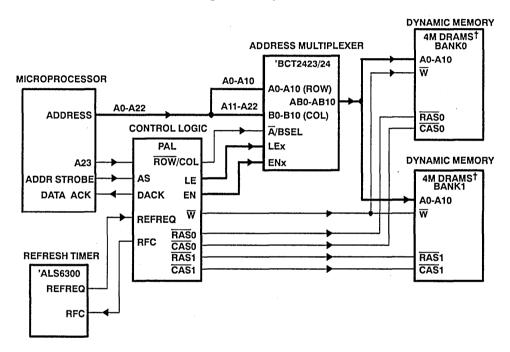

In addition, this Data Book contains design specification data for all six devices previously listed. Three application reports are also included: *Support NuBus™ Block Slave Transfers Using Texas Instruments SN74ACT2440, SN74BCT2420, and SN74ALS2442, Designing Simple NuBus™ Slave-Only Applications Using Texas Instruments SN74ACT2440 and SN74BCT2420, and Memory Interleave/ Interface Applications using Texas Instruments SN74BCT2423 and SN74BCT2424.*

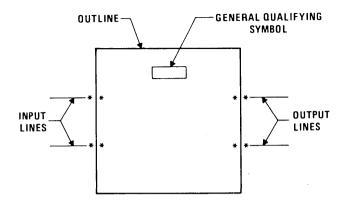

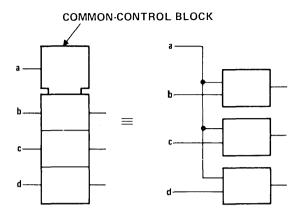

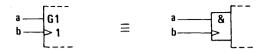

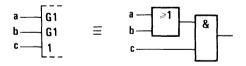

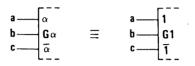

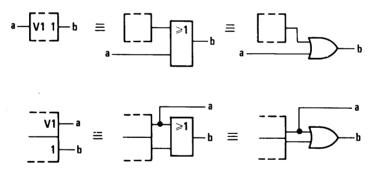

A section on the development of logic symbols to meet both ANSI/IEEE Std 91-1984 and IEC Publication 617-12 is included for the reader's better understanding.

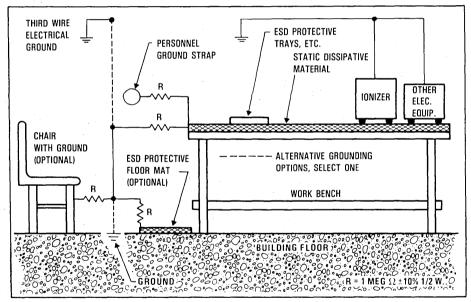

The ESD Guidelines utilized by TI are discussed in another section for the reader's better understanding.

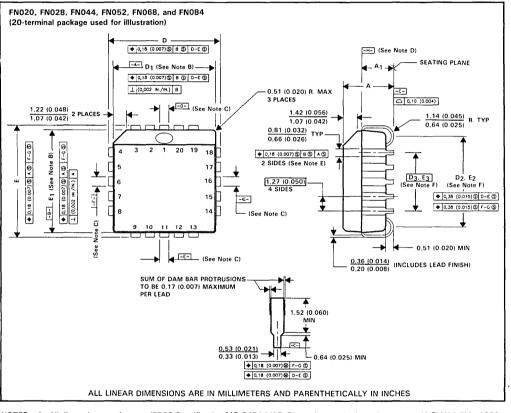

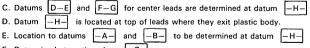

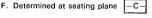

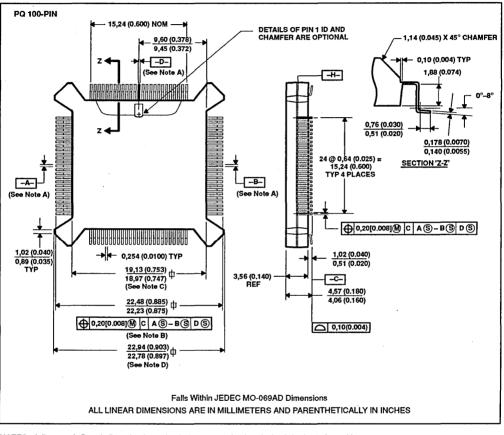

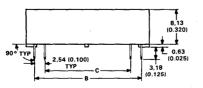

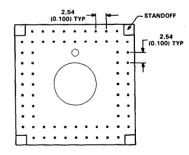

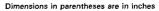

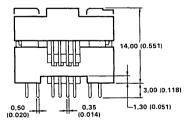

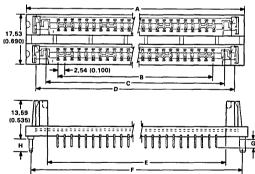

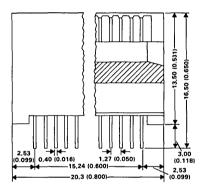

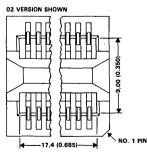

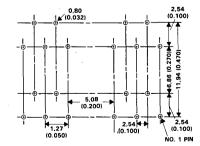

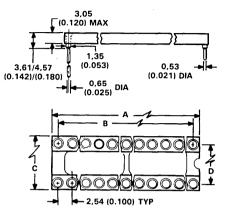

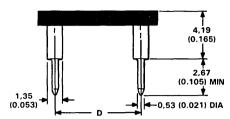

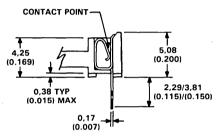

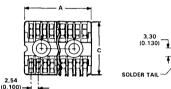

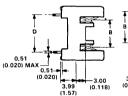

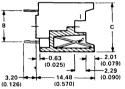

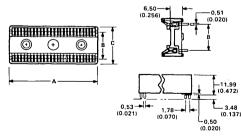

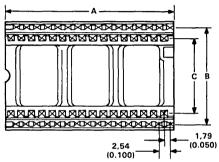

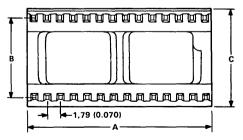

Package dimensions are given in the Mechanical Data section of the book in metric measurement (and parenthetically in inches).

Complete technical data for any Texas Instruments semiconductor product is available from your nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at 1-800-232-3200.

<sup>†</sup> Macintosh Coprocessor Platform

NuBus is a trademark of Texas Instruments Incorporated.

vi

## Contents

|                                | Page |

|--------------------------------|------|

| Alphanumeric Index             | 1-3  |

| Ordering Instructions          | 1-5  |

| Glossary                       | 1-7  |

| Timing Interval Conventions    | 1-11 |

| Explanation of Function Tables | 1-15 |

| Timing Diagram Conventions     | 1-17 |

| Basic Data Sheet Structure     | 1-19 |

| SN74ACT2441             | 2-67 | SN74BCT2423<br>SN74BCT2424<br>SN74BCT2425 | 2-13 |

|-------------------------|------|-------------------------------------------|------|

| SN74AL32442 SN74BCT2420 |      | 3N74BCT2425                               | 2-23 |

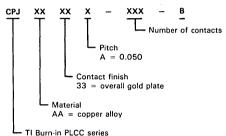

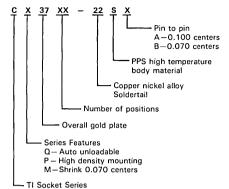

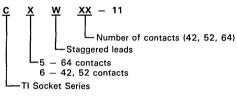

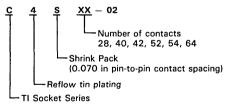

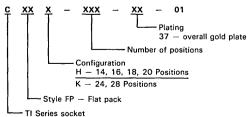

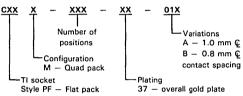

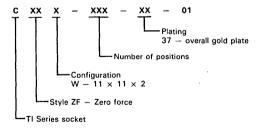

Factory orders for NuBus™ products described in this book should include a three-part type number as explained in the following example:

|                           | SN 74BCT2420 F | N, |

|---------------------------|----------------|----|

| Prefix ————               | / / /          |    |

| SN Standard Prefix        |                |    |

| Circuit Description ————— | / /            |    |

| 4 to 10 Characters        |                |    |

| Package                   | /              |    |

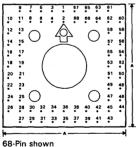

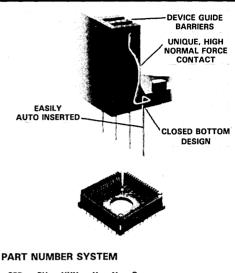

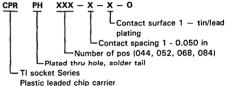

| FN Plastic Chip Carrier   |                |    |

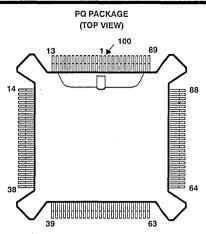

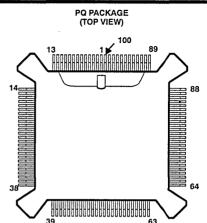

PQ Plastic Quad Flat

NuBus is a trademark of Texas Instruments Incorporated.

1-6

.

•

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

Ci Input capacitance The internal capacitance at an input of the device.

#### Co Output capacitance

The internal capacitance at an output of the device.

fmax Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

#### ICC Supply current

The current into<sup>†</sup> the VCC supply terminal of an integrated circuit.

#### ICCH Supply current, outputs high

The current into<sup>†</sup> the V<sub>CC</sub> supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the high level.

#### ICCL Supply current, outputs low

The current into<sup>†</sup> the V<sub>CC</sub> supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the low level.

#### IIH High-level input current

The current into<sup>†</sup> an input when a high-level voltage is applied to that input.

#### IL Low-level input current

The current into<sup>†</sup> an input when a low-level voltage is applied to that input.

#### IOH High-level output current

The current into<sup> $\dagger$ </sup> an output with input conditions applied that, according to the product specification, will establish a high level at the output.

#### IOL Low-level output current

The current into<sup> $\dagger$ </sup> an output with input conditions applied that, according to the product specification, will establish a low level at the output.

#### IOS (IO) Short-circuit output current

The current into<sup> $\dagger$ </sup> an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

<sup>†</sup>Current out of a terminal is given as a negative value.

## GLOSSARY Symbols, terms, and definitions

## IOZH Off-state (high-impedance-state) output current (of a three-state output) with high-level voltage applied

The current flowing into  $^{\dagger}$  an output having three-state capability with input conditions established that, according to the production specification, will establish the high-impedance state at the output and with a high-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a low level if it were enabled.

## IOZL Off-state (high-impedance-state) output current (of a three-state output) with low-level voltage applied

The current flowing into  $^{\dagger}$  an output having three-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a low-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a high level if it were enabled.

#### ta Access time

The time interval between the application of a specified input pulse and the availability of valid signals at an output.

#### tdis Disable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state. ( $t_{dis} = t_{PHZ}$  or  $t_{PLZ}$ ).

#### ten Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low). ( $t_{en} = t_{PZH}$  or  $t_{PZL}$ .)

#### tf Fall time

The time interval between two reference points (90% and 10% unless otherwise specified) on a waveform that is changing from the defined high level to the defined low level.

#### th Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

#### tpd Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. ( $t_{pd} = t_{PHL}$  or  $t_{PLH}$ ).

<sup>†</sup>Current out of a terminal is given as a negative value.

#### tpHL Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

#### tpHZ Disable time (of a three-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

#### tPLH Propagation delay time, low-to-high-level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

#### tpLZ Disable time (of a three-state output) from low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

#### tPZH Enable time (of a three-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

#### tpzL Enable time (of a three-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

#### tr Rise time

The time interval between two reference points (10% and 90% unless otherwise specified) on a waveform that is changing from the defined low level to the defined high level.

#### t<sub>su</sub> Setup time

tŧ

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

#### Transition time (general)

The time interval between two reference points (10% and 90% unless otherwise specified) on a waveform that is changing from the defined low level to the defined high level (rise time) or from the defined high level to the defined low level (fall time).

#### tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

## GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

#### VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### VIL Low-level input voltage

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### VOH High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

#### VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

## TIMING INTERVAL CONVENTIONS

New or revised data sheets in this book use letter symbols in accordance with standards recently adopted by JEDEC, the IEEE, and the IEC. Two basic forms are used. The first form is usually used in this book when intervals can easily be classified as access, cycle, disable, enable, hold, refresh, setup, transition, or valid times and for pulse durations. The second form can be used generally but in this book is used primarily for time intervals not easily classifiable. The second (unclassified) form will be described first. Since some manufacturers use this form for all time intervals, symbols in the unclassified form are given with the examples for most of the classified time intervals.

#### Unclassified time intervals

Generalized letter symbols can be used to identify almost any time interval without classifying it using traditional or contrived definitions. Symbols for unclassifed time intervals identify two signal events listed in from-to sequence using the format:

#### tAB-CD

Subscripts A and C indicate the names of the signals for which changes of state or level or establishment of state or level constitute signal events assumed to occur first and last, respectively, that is, at the beginning and end of the time interval. Every effort is made to keep the A and C subscript length down to one letter, if possible (e.g., R for READ and W for WRITE).

Subscripts B and D indicate the direction of the transitions and/or the final states or levels of the signals represented by A and C, respectively. One or two of the following is used:

- H = high or transition to high

- L = low or transition to low

- V = a valid steady-state level

- X = unknown, changing, or "don't care" level

- Z = high-impedance (off) state

The hyphen between the B and C subscripts is omitted when no confusion is likely to occur.

#### Classified time intervals (general comments, specific times follow)

Because of the information contained in the definitions, frequently the identification of one or both of the two signal events that begin and end the intervals can be significantly shortened compared to the unclassified forms. For example, it is not necessary to indicate in the symbol that an access time ends with valid data at the output. However, if both signals are named (e.g., in a hold time), the from-to sequence is maintained.

#### Access time

The time interval between the application of a specific input pulse and the availability of valid signals at an output.

Example symbology:

| Classified                            | Unclassified | Description                        |

|---------------------------------------|--------------|------------------------------------|

| <sup>t</sup> a(A)                     | tAVQV        | Access time from address           |

| <sup>t</sup> a(S), <sup>t</sup> a(CS) | tSLQV        | Access time from chip select (low) |

#### Cycle time

The time interval between the start and end of a cycle.

NOTE: The cycle time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval that must be allowed for the digital circuit to perform a specified function (e.g., read, write, etc.) correctly.

Example symbology:

| Classifed                             | Unclassified         | Description      |

|---------------------------------------|----------------------|------------------|

| <sup>t</sup> c(R), <sup>t</sup> c(rd) | <sup>t</sup> AVAV(R) | Read cycle time  |

| <sup>t</sup> c(W)                     | <sup>t</sup> AVAV(W) | Write cycle time |

#### Disable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state.

Example symbology:

| Classified          | Unclassified      | Description                                  |

|---------------------|-------------------|----------------------------------------------|

| <sup>t</sup> dis(S) | <sup>t</sup> SHQZ | Output disable time after chip select (high) |

| <sup>t</sup> dis(W) | <sup>t</sup> WLQZ | Output disable time after write enable (low) |

These symbols supersede the older forms tPVZ or tPXZ.

#### Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low).

Example symbology:

| Classified           | Unclassifed | Description                              |

|----------------------|-------------|------------------------------------------|

| t <sub>en</sub> (SL) | tSLQV       | Output enable time after chip select low |

These symbols supersede the older form tpzv.

#### Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

Example symbology:

| Classified        | Unclassified | Description                       |

|-------------------|--------------|-----------------------------------|

| <sup>t</sup> h(D) | tWHDX        | Data hold time (after write high) |

NOTE: The from-to sequence in the order of subscripts in the unclassified form is maintained in the classified form. In the case of hold times, this causes the order to seem reversed from what would be suggested by the terms.

#### Pulse duration (width)

The time interval between the specified reference points on the leading and trailing edges of the pulse waveform.

Example symbology:

| Classified        | Unclassified      | Description          |

|-------------------|-------------------|----------------------|

| <sup>t</sup> w(W) | <sup>t</sup> WLWH | Write pulse duration |

| <sup>t</sup> w(R) | <sup>t</sup> RLRH | Read pulse duration  |

#### Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

Example symbology:

| Classified          | Unclassified | Description                         |

|---------------------|--------------|-------------------------------------|

| t <sub>su</sub> (D) | tdvwh        | Data setup time (before write high) |

#### Transition times (also called rise and fall times)

The time interval between two reference points (10% and 90% unless otherwise specified) on the same waveform that is changing from the defined low level to the defined high level (rise time) or from the defined high level to the defined low level (fall time).

Example symbology:

| Classified | Unclassified | Description               |

|------------|--------------|---------------------------|

| tt         |              | Transition time (general) |

#### Valid time

(a) General

The time interval during which a signal is (or should be) valid.

(b) Output data-valid time

The time interval in which output data continues to be valid following a change of input conditions that could cause the output data to change at the end of the interval.

Example symbology:

| Classified         | Unclassified | Description                                    |

|--------------------|--------------|------------------------------------------------|

| t <sub>v</sub> (A) | taxox        | Output data valid time after change of address |

This supersedes the older form  $t_{PVX}$ .

· · ·

. .

1-14

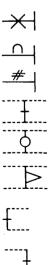

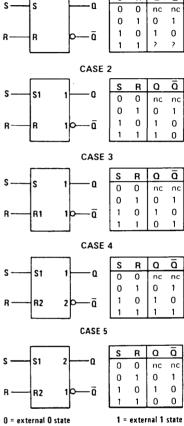

| The followin   | ng sy | mbols are used in function tables on TI data sheets:                                                                          |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| н              | =     | high level (steady state)                                                                                                     |

| L              | =     | low level (steady state)                                                                                                      |

| t              | =     | transition from low to high level                                                                                             |

| t              | =     | transition from high to low level                                                                                             |

| <b>→</b>       | =     | value/level or resulting value/level is routed to indicated destination                                                       |

|                | =     | value/level is re-entered                                                                                                     |

| х              | =     | irrelevant (any input, including transitions)                                                                                 |

| Z              | =     | off (high-impedance) state of a 3-state-output                                                                                |

| ah             | =     | the level of steady-state inputs at inputs A through H respectively                                                           |

| Q <sub>0</sub> | =     | level of Q before the indicated steady-state input conditions were established                                                |

| <u>a</u> 0     | =     | complement of ${\tt Q}_0$ or level of $\overline{\tt Q}$ before the indicated steady-state input conditions were established  |

| Qn             | =     | level of Q before the most recent active transition indicated by $\downarrow$ or $\uparrow$                                   |

| 5              | =     | one high-level pulse                                                                                                          |

|                | =     | one low-level pulse                                                                                                           |

| TOGGLE         | =     | each output changes to the complement of its previous level on each active transition indicated by $\downarrow$ or $\uparrow$ |

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or I, this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q_0}$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\neg \neg \neg$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

Shift registers provide a good example of the features of a function table. The function table of a shift register embodies all of the symbols used in most function tables. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

| INPUTS |      |    |       |      |       |          |   |   | OUT | PUTS            |                 |                 |                 |

|--------|------|----|-------|------|-------|----------|---|---|-----|-----------------|-----------------|-----------------|-----------------|

|        | MODE |    | CLOCK | SE   | RIAL  | PARALLEL |   |   |     | •               |                 | 0               |                 |

| CLEAR  | S1   | SO |       | LEFT | RIGHT | A        | В | С | D   | QA              | Ω <sub>B</sub>  | αc              | ۵D              |

| L      | х    | х  | X     | X    | х     | X        | х | х | х   | L               | L               | L               | L               |

| н      | х    | х  | L     | X    | х     | X        | х | × | х   | 0 <sub>A0</sub> | Q <sub>B0</sub> | QCO             | Q <sub>D0</sub> |

| н      | н    | н  | † ↑   | X    | х     | a        | b | с | d   | а               | b               | с               | d               |

| н      | L    | н  | t t   | X X  | н     | X        | х | х | х   | н               | ۵ <sub>An</sub> | QBn             | QCn             |

| н      | L    | н  | t t   | X    | · L   | X        | х | Х | х   | L               | ۵ <sub>An</sub> | QBn             | QCn             |

| н      | н    | L  | 1 1   | н    | х     | X        | х | х | х   | Q <sub>Bn</sub> | QCn             | Q <sub>Dn</sub> | н               |

| н      | н    | L  | t t   | L    | х     | x        | х | х | х   | 0 <sub>Bn</sub> | QCn             | QDn             | L               |

| н      | L    | L  | .X    | x    | х     | х        | Х | х | х   | Q <sub>A0</sub> | 0 <sub>B0</sub> | 0 <sub>C0</sub> | 0 <sub>D0</sub> |

FUNCTION TABLE

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $Q_A$ , data entered at B will be at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shiftright serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$  respectively, and the data previously at  $Q_D$  is no longer in the register. The entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shiftleft serial input and the shifting of previously entered data one bit; data previously at Q<sub>B</sub> is now at Q<sub>A</sub>, the previous levels of Q<sub>C</sub> and Q<sub>D</sub> are now at Q<sub>B</sub> and Q<sub>C</sub>, respectively, and the data previously at Q<sub>A</sub> is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both mode inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

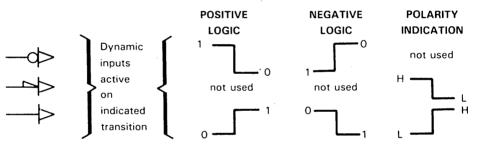

## TIMING DIAGRAM CONVENTIONS

#### MEANING

#### TIMING DIAGRAM SYMBOL

#### INPUT FORCING FUNCTIONS

#### OUTPUT RESPONSE FUNCTIONS

\_\_\_\_\_

Must be steady high or lowWill be steady high or lowHigh-to-low changes permittedWill be changing from high to low some time during<br/>designated intervalLow-to-high changes permittedWill be changing from low to high sometime during<br/>designated intervalDon't CareState unknown or changing(Does not apply)Centerline represents high-impedance (off) state.

The front page of the data sheet begins with a list of key features such as organization, interface, compatibility, operation, and technology. In addition, the top view of the device is shown with the pinout provided. Next, a general description of the device, system interface considerations, and elaboration on other device characteristics are presented. The next section is an explanation of the device's operation which includes the function of each pin (i.e., the relationship between each input/output and a given type of application).

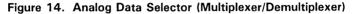

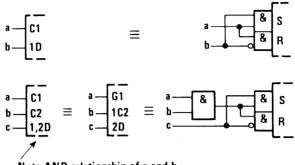

Augmenting the descriptive text, there appears a logic symbol prepared in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12 and explained in Section 4 of this book. Following the symbol is usually a functional block diagram or a logic diagram. Usually, the next few pages contain the absolute maximum ratings (e.g., voltage supplies, input voltage, and temperature) applicable over the operating free-air temperature range. If the device is used outside of these values, it may be permanently destroyed or at least it would not function as intended. Next, are the recommended operating conditions, (e.g., supply voltages, input voltages, and operating temperature). These devices are specified to work reliably and to meet all data sheet parameters when operated in accordance with the recommended operating conditions and within the specified timing. If the device is operated outside of these limits (minimum/maximum), it is no longer specified to meet the data sheet parameters. Operation beyond the absolute maximum ratings can result in catastrophic failures.

The next section provides a table of electrical characteristics over full ranges of recommended operating conditions (e.g., input and output currents, output voltages, etc.). These are presented as minimum, typical, and maximum values. Typical values are representative of operation at an ambient temperature of  $T_A = 25 \,^{\circ}C$  with all power supply voltages at nominal value.

The next few tables involve the device timing characteristics. The parameters are presented as minimum, typical (or nominal), and maximum. The switching characteristics over recommended supply voltage range are device performance characteristics inherent to device operation once the inputs are applied. These parameters are specified for the test conditions given. The timing requirements over recommended supply voltage range and operating free-air temperature indicate the device control requirements such as hold times, setup times, and transition times. These values are referenced to the relative positioning of signals on the timing diagrams that follow. The interrelationship of the timing requirements to the switching characteristics is illustrated in the parameter measurement information section.

At the end of a data sheet additional applications information may be provided such as how to use the device, graphs of electrical characteristics, or other data on electrical characteristics.

## Contents

|             |                                                  | Page  |

|-------------|--------------------------------------------------|-------|

| SN74BCT2420 | NuBus™ Address/Data Transceivers and             |       |

|             | Registers                                        | 2-3   |

| SN74BCT2423 | 16-Bit Latched Multiplexer/Demultiplexer Bus     |       |

|             | Transceivers                                     | 2-13  |

| SN74BCT2424 | 16-Bit Latched Multiplexer/Demultiplexer Bus     |       |

|             | Transceivers                                     | 2-13  |

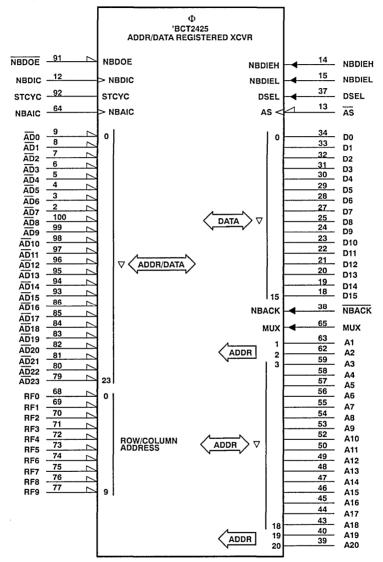

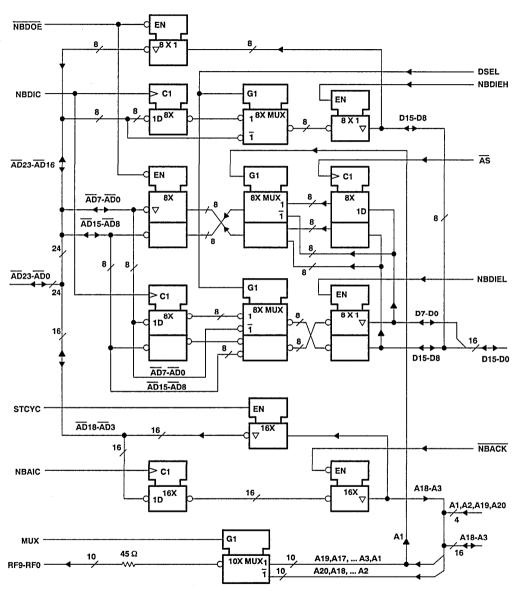

| SN74BCT2425 | MCP NuBus™ Address/Data Transceivers and         |       |

|             | Registers                                        | 2-23  |

| SN74ACT2440 | NuBus <sup>™</sup> Interface Controller          | 2-35  |

| SN74ACT2441 | MCP NuBus <sup>™</sup> Interface Controller      | 2-67  |

| SN74ALS2442 | NuBus <sup>™</sup> Block Slave Address Generator | 2-121 |

|             |                                                  |       |

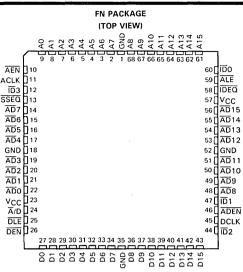

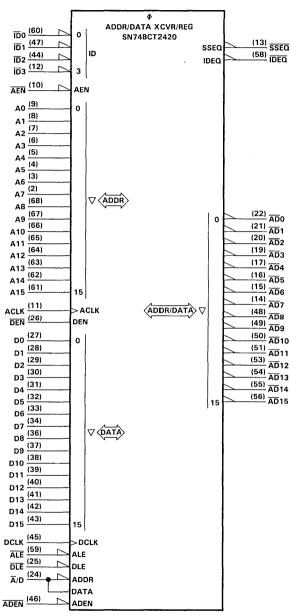

D3159, NOVEMBER 1988-REVISED JANUARY 1989

- Designed for NuBus<sup>™</sup> Interface Applications

- Conforms to ANSI/IEEE Std 1196-1987

- On-Chip Comparator Provides I/D Slot Identification

- Multiplexed Real-Time and Latched Address/Data

- Designed to Operate with SN74ACT2440 NuBus<sup>™</sup> Controller

- BiCMOS Design Substantially Reduces Standby Current

- Dependable Texas Instruments Quality and Reliability

#### description

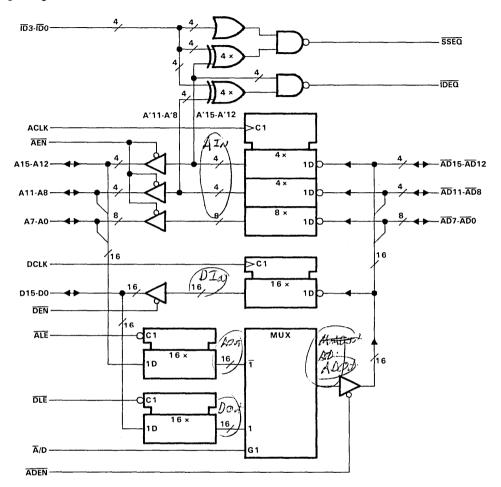

The 'BCT2420 consists of bus transceiver circuits, D-type flip-flops, latches, and control circuitry arranged for multiplexed transmission of address and data information in NuBus™

applications. An on-chip comparator has been included to detect when a NuBus™ transfer cycle is requesting the local board. The device conforms to ANSI/IEEE Std 1196-1987 and operates with Texas Instruments SN74ACT2440 NuBus™ Controller. In addition, the device is easily configured around ASIC or other PAL®-based controllers.

The 'BCT2420 was designed using Texas Instruments BiCMOS process, which features bipolar drive characteristics and greatly reduces the standby power of the device when disabled. This feature is especially valuable when the device is not performing a NuBus<sup>™</sup> transaction.

The AEN, DEN and ADEN inputs control the transceiver functions. Three 16-bit I/O ports, A15-AO, D15-D0, and AD15-AD0, provide for address and data transfer. When the NuBus<sup>™</sup> performs a write cycle to the local board, address information is saved on the rising edge of ACLK. During the last portion of the NuBus<sup>™</sup> write cycle, data information is saved on the rising edge of DCLK.

When the local board is performing a write to the NuBus<sup>™</sup>, address and data is multiplexed onto the NuBus<sup>™</sup> via the A/D line. Address and data can be latched by using the ALE and DLE input lines respectively.

The IDEQ output is used to signal that the local board is being requested by the NuBus<sup>™</sup>. This output is typically fed to the NuBus<sup>™</sup> controller. IDEQ goes active (Iow) when AD15-AD12 are low and AD11-AD8 match ID3-ID0. IDEQ stays valid until the next address clock (ACLK) occurs. Internal 10-kΩ pull-up resistors are included on the ID3-ID0 inputs.

The SSEQ output is used to signal the local board that super-slot addresses are being requested. This output is active (low) whenever AD15-AD12 are equal to ID3-ID0, except when ID3-ID0 are all low.

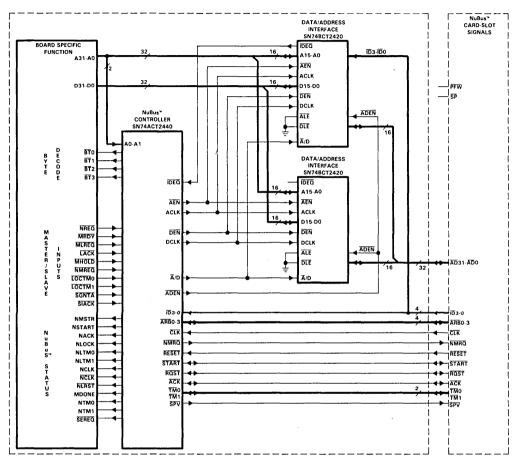

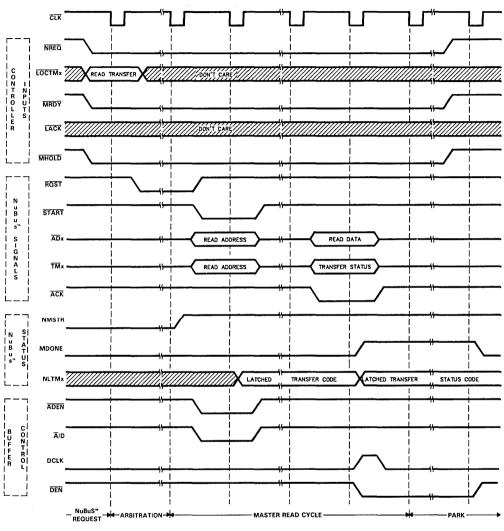

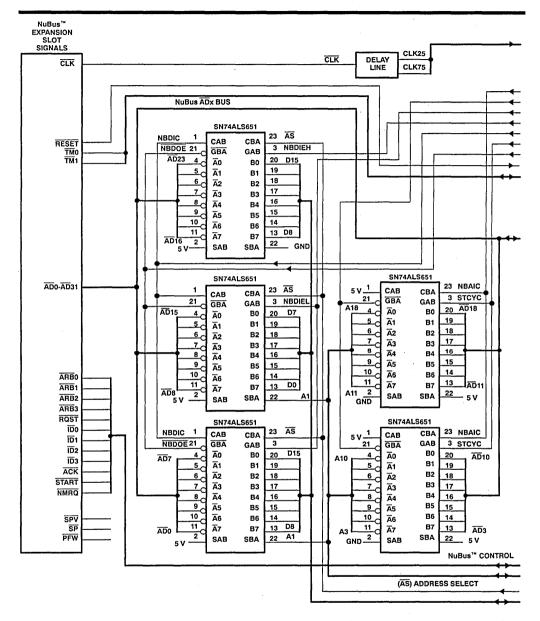

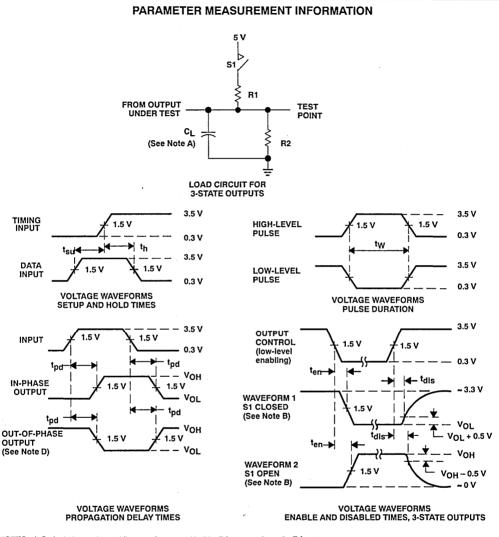

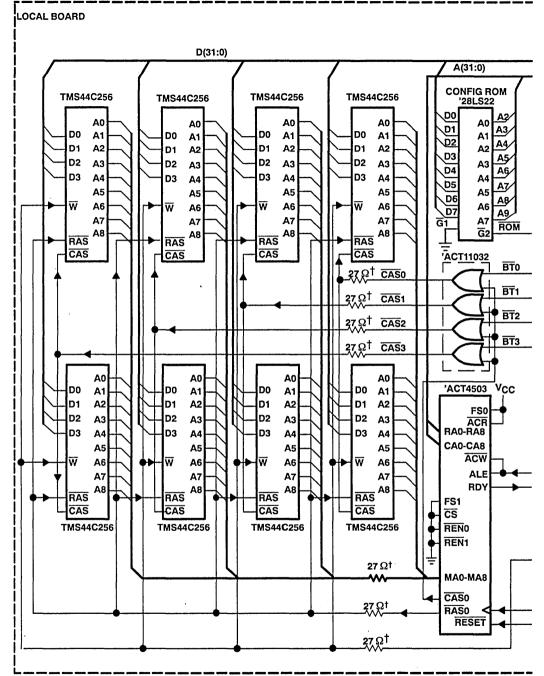

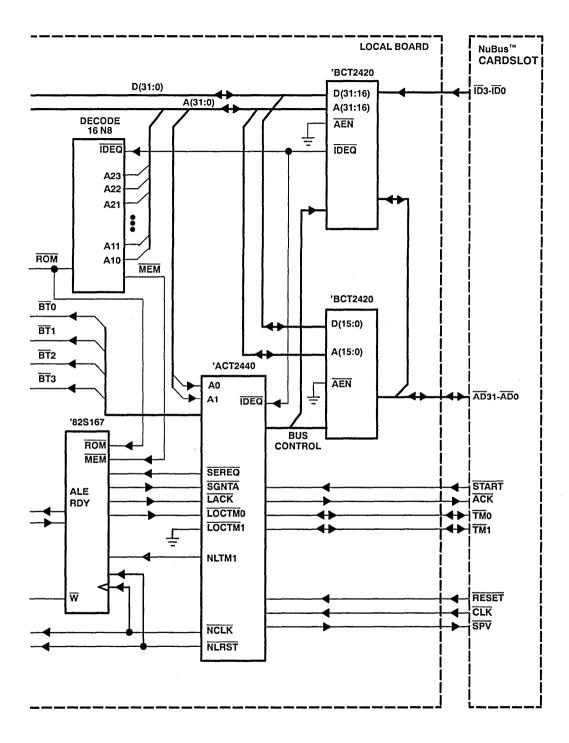

In typical NuBus™ applications, two devices are required to provide the full 32-bit address/data path. Refer to the typical NuBus™ interface diagram on page 9 for additional information.

The SN74BCT2420 is characterized for operation from 0 °C to 70 °C.

NuBus is a trademark of Texas Instruments Incorporated. PAL is a registered trademark of Monolithic Memories Inc.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

| FUNCTION TABLES |                               |   |   |   |   |                |  |  |  |

|-----------------|-------------------------------|---|---|---|---|----------------|--|--|--|

|                 | OUTPUTS                       |   |   |   |   |                |  |  |  |

| A15-A0          | 15-A0 D15-D0 ALE DLE A/D ADEN |   |   |   |   |                |  |  |  |

| н               | x                             | L | x | L | L | L              |  |  |  |

| L               | х                             | L | х | L | L | н              |  |  |  |

| х               | х                             | н | х | L | L | 0 <sub>0</sub> |  |  |  |

| х               | н                             | х | L | н | L | L              |  |  |  |

| X               | L                             | х | L | н | L | н              |  |  |  |

| х               | х                             | х | н | н | L | ۵ <sub>0</sub> |  |  |  |

| х               | х                             | х | х | х | н | z              |  |  |  |

|          | INPUTS     |          | OUTPUTS        |

|----------|------------|----------|----------------|

| AD15-AD0 | ACLK, DCLK | AEN, DEN | A15-A0, D15-D0 |

| н        | t          | L        | L              |

| L        | t          | L        | н              |

| x        | L          | L        | 0 <sub>0</sub> |

| ×        | ×          | н        | z              |

| AD15-AD12  | ID3-ID0 | SSEQ |

|------------|---------|------|

| EQ ID3-ID0 | NE O    | L    |

| NE ÎD3-ÎDO | х       | н    |

| х          | EQ 0    | н    |

| AD15-AD12 | AD11-AD8   | IDEQ |

|-----------|------------|------|

| EO O      | EQ ID3-ID0 | L    |

| x         | NE ID3-ID0 | н    |

| NE O      | X          | н    |

NOTE: Symbol ' $\Omega_0$ ' denotes previous logic state preserved. Symbol 'Z' denotes high-impedance state.

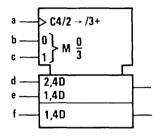

logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984.

logic diagram

2-6

|          | TERMINAL FUNCTIONS                                                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME | DESCRIPTION                                                                                                                                           |

| A15-A0   | Address Bus. This 16-bit I/O port is connected to the local board's address bus. When information is transferred between                              |

| AT5-AU   | this port and the NuBus <sup>™</sup> port (AD15-AD0), the data is inverted to conform to NuBus <sup>™</sup> specifications.                           |

| ACLK     | Address Clock. This input saves the address portion of NuBus" read or write cycles. Data present at the AD15-AD0                                      |

| ACER     | inputs is clocked into the address register on the low-to-high transition of ACLK.                                                                    |

|          | Address/Data Select. This input controls the address/data multiplexer. When $\overline{A}$ /D is driven low, the local address port,                  |

| Ā/D      | A15-A0, is selected as input to the AD15-AD0 outputs. When A/D is taken high, the local data port, D15-D0, is selected                                |

|          | as input to the AD15-AD0 outputs.                                                                                                                     |

| AD15-AD0 | Address/Data Port. This 16-bit active-low I/O port directly interfaces to the NuBus" address/data lines. These lines are                              |

|          | multiplexed to carry address information at the beginning of a NuBus <sup>w</sup> cycle and data information later in the cycle.                      |

| ADEN     | Address/Data Output Enable. This active-low input enables the $\overline{AD15}$ - $\overline{AD0}$ outputs. When $\overline{ADEN}$ is taken high, the |

|          | AD15-AD0 outputs are in the high-impedance state, allowing input from the NuBus™.                                                                     |

| AEN      | Address Enable. This active-low input enables the local address outputs, A15-A0, to place data onto the local board.                                  |

|          | When AEN is taken high, the A15-A0 outputs are in the high-impedance state, allowing input from the local address bus.                                |

|          | Address Latch Enable. This active-low input controls the latch that holds the address received from the local address                                 |

| ALE      | bus, A15-A0. When ALE is low, the latch is transparent. When ALE is taken high, the address present at the A15-A0                                     |

|          | inputs is latched and remains latched while ALE is held high.                                                                                         |

| D15-D0   | Data Bus. This 16-bit I/O port is connected to the local board's data bus. When information is transferred between this                               |

|          | port and the NuBus <sup>™</sup> port (AD15-AD0), the data is inverted to conform to NuBus <sup>™</sup> specifications.                                |

| DCLK     | Data Clock. This input saves the data portion of NuBus™ write cycles. Data present at the AD15-AD0 inputs is clocked                                  |

|          | into the data register on the low-to-high transition of DCLK.                                                                                         |

| DEN      | Data Enable. This active-low input enables the local data port outputs, D15-D0, to place data onto the local board. When                              |

|          | DEN is taken high, the D15-D0 outputs are in the high-impedance state, allowing input from the local board.                                           |

|          | Data Latch Enable. This active-low input controls the latch that holds the data received from the local data bus, D15-D0.                             |

| DLE      | When DLE is low, the latch is transparent. When DLE is taken high, the data present at the D15-D0 inputs is latched                                   |

|          | and remains latched while DLE is held high.                                                                                                           |

|          | Card-Slot Identification. These four inputs accept binary-coded location information for each NuBus <sup>™</sup> slot position on                     |

| ĪD3-ĪD0  | the backplane. These four lines are typically hard-wired logic levels unique to each NuBus™ slot connector. For convenient                            |

|          | implementation, the inputs have internal 10-k $\Omega$ pull-up resistors that ensure the logic high level when the inputs are                         |

|          | left open-circuited. The internal comparator uses these inputs to identify when the local hardware card is being accessed.                            |

|          | Identification Equal. This active-low output is used to signal that the local board is being accessed by the NuBus <sup>™</sup> , IDEQ                |

| IDEQ     | goes low whenever AD15-AD12 are low and AD11-AD8 match ID3-ID0. Since the internal comparator uses data from                                          |

|          | the address register, the address register must be clocked before the local board samples IDEQ. IDEQ is valid for the                                 |

|          | entire NuBus™ cycle after ACLK.                                                                                                                       |

|          | Super-Slot Equal. This active-low output is used to signal the local board that super-slot addresses are being requested                              |

| SSEQ     | in the super-slot mode. SSEQ goes low when AD15-AD12 match ID3-ID0 and ID3-ID0 are not all low. Since the internal                                    |

|          | comparator uses data from the address register, the address register must be clocked before the local board samples                                   |

|          | SSEQ. SSEQ is valid for the entire NuBus™ cycle after ACLK.                                                                                           |

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, VCC (see Note 1) 7 V           |

|------------------------------------------------|

| Input voltage (all inputs and I/O ports) 5.5 V |

| Operating free-air temperature range           |

| Storage temperature range                      |

<sup>†</sup>Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "recommended operating conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

#### recommended operating conditions

|                 | P                                     | ARAMETER                                        | MIN  | NOM               | MAX  | UNIT |  |

|-----------------|---------------------------------------|-------------------------------------------------|------|-------------------|------|------|--|

| Vcc             | Supply voltage                        |                                                 | 4.5  | 5                 | 5.5  | ·V   |  |

| VIH             | High-level input voltage              |                                                 | 2    |                   |      | v    |  |

| VIL             | Low-level input voltage               |                                                 |      |                   | 0.8  | v    |  |

| юн              | tlick lovel even evenes               | Ax, Dx, ADx outputs                             |      |                   | - 15 |      |  |

|                 | High-level output current             | SSEQ, IDEQ outputs                              |      |                   | -2.6 | mA   |  |

| 1               |                                       | Ax, Dx, ADx outputs                             |      |                   | 24   | mA   |  |

| IOL             | Low-level output current              | SSEQ, IDEQ outputs                              |      |                   | 16   | mA   |  |

| fclock          | Clock frequency                       |                                                 | 0    |                   | 40   | MHz  |  |

|                 |                                       | ACLK, DCLK high                                 | 12.5 |                   |      | ns   |  |

| tw              | Pulse duration                        | ACLK, DCLK low                                  | 12.5 |                   |      |      |  |

|                 |                                       | ALE, DLE low                                    | 12.5 |                   |      |      |  |

|                 |                                       | ADx before ACLK1, DCLK1                         | 5    |                   |      | ns   |  |

| t <sub>su</sub> | Setup time                            | Ax before ALEt                                  | 5    | · · · · · · · · · |      |      |  |

|                 |                                       | Dx before DLEt                                  | 5    |                   |      |      |  |

|                 | · · · · · · · · · · · · · · · · · · · | ADx after ACLK <sup>†</sup> , DCLK <sup>†</sup> | 2    |                   |      |      |  |

| th              | Hold time                             | Ax after ALEt                                   | 2    |                   |      | ns   |  |

|                 |                                       | Dx after DLE1                                   | 2    |                   |      | 1    |  |

| TA              | Operating free-air temperature        |                                                 | 0    |                   | 70   | °C   |  |

|      | PARAMETER        | TEST CONDITIONS                                  | MIN                   | TYP <sup>†</sup> | MAX   | UNIT |

|------|------------------|--------------------------------------------------|-----------------------|------------------|-------|------|

| VIK  |                  | $V_{CC} = 4.5 V$ , $I_{I} = -18 mA$              |                       |                  | - 1.2 | V    |

|      |                  | $V_{CC} = 4.5 V$ to 5.5 V, $I_{OH} = -400 \mu A$ | V <sub>CC</sub> - 1.5 |                  |       |      |

|      | Ax, Dx, ADx      | $V_{CC} = 4.5 V$ , $I_{OH} = -3 mA$              | 2.8                   | 3.6              |       | 7    |

| Val  |                  | $V_{CC} = 4.5 V$ , $I_{OH} = -15 mA$             | 2                     |                  |       | v    |

| ∨он  | SSEQ, IDEQ       | $V_{CC} = 4.5 V$ to 5.5 V, IOH = $-400 \mu A$    | V <sub>CC</sub> -2    |                  |       | v    |

|      | 33EQ, IDEQ       | $V_{CC} = 4.5 V$ , $I_{OH} = -2.6 mA$            | 2.4                   | 3.2              |       |      |

| VOL  | Ax, Dx, ADx      | $V_{CC} = 4.5 V$ , $I_{OL} = 12 mA$              |                       | 0.25             | 0.4   | v    |

|      | Ax, Dx, ADx      | $V_{CC} = 4.5 V$ , $I_{OL} = 24 mA$              |                       | 0.35             | 0.5   |      |

|      | SSEQ, IDEQ       | $V_{CC} = 4.5 V$ , $I_{OL} = 8 mA$               |                       | 0.25             | 0.4   |      |

|      | 33EQ, IDEQ       | $V_{CC} = 4.5 V$ , $I_{OL} = 16 mA$              |                       | 0.35             | 0.5   |      |

| կ    |                  | $V_{CC} = 5.5 V, V_{I} = 5.5 V$                  |                       |                  | 100   | μA   |

|      | AEN, DEN, ADEN   |                                                  |                       |                  | 20    |      |

| чн‡  | <u>ID</u> 3-ID0  | $V_{CC} = 5.5 V, V_{I} = 2.7 V$                  |                       |                  | - 400 | μA   |

|      | All other inputs |                                                  |                       |                  | - 100 |      |

| 1 İ  | ĪD3-ĪD0          |                                                  |                       |                  | - 750 |      |

| łı∟‡ | All other inputs |                                                  | - 200                 |                  |       | μA   |

| los§ |                  | $V_{CC} = 5.5 V, V_{O} = 0 V$                    | 60                    |                  | - 225 | mA   |

|      | Enabled          | $V_{CC} = 5.5 V, V_{IL} = 0.5 V, V_{IH} = 3 V,$  |                       | 110              | 160   |      |

| lcc  | Disabled         | Outputs open                                     |                       | 30               | 40    | mA   |

#### electrical characteristics over recommended operating free-air temperature range

<sup>†</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C. <sup>‡</sup>For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the off-state output current.

§Not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second.

# SN74BCT2420 NuBus™ ADDRESS/DATA TRANSCEIVERS AND REGISTERS

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                   | PARAMETER                                                                             | LOA                                                                              | D COND | TIONS                  | MIN    | TYPT | мах | UNIT |

|-------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------|------------------------|--------|------|-----|------|

|                   | PARAMETER                                                                             | R1, R2, and RL                                                                   | CL     | LOAD CIRCUIT           | IVILIN | 116. | WAA | UNIT |

| f <sub>ma</sub> , | Maximum clock frequency                                                               |                                                                                  |        |                        | 40     |      |     | MHz  |

| t <sub>pd</sub>   | Propagation time, ACLK <sup>†</sup> to Ax ( $\overline{AEN} = L$ )                    | $R1 = 500 \Omega,$<br>$R2 = 500 \Omega$                                          | 50 pF  | S1 Open <sup>‡</sup>   |        | 9    | 16  | ns   |

| tpd               | Propagation time, DCLK <sup>†</sup> to Dx ( $\overline{DEN} = L$ )                    | R1 = 500 Ω,<br>R2 = 500 Ω                                                        | 50 pF  | S1 Open‡               |        | 9    | 16  | ns   |

| t <sub>pd</sub>   | Propagation time, Ax to $\overline{ADx}$ ( $\overline{ALE} = L, \overline{A}/D = L$ ) | R1 = 270 Ω, R2 = 470 Ω                                                           | 300 pF | S1 Closed <sup>§</sup> |        | 10   | 18  | ns   |

| t <sub>pd</sub>   | Propagation time, Dx to $\overline{AD}x$ ( $\overline{DLE} = L, \overline{A}/D = H$ ) | R1 = 270 Ω, R2 = 470 Ω                                                           | 300 pF | S1 Closed <sup>§</sup> |        | 11   | 18  | ns   |

| t <sub>pd</sub>   | Propagation time, $\overline{ALE}$ low to $\overline{ADx}$ (A/D = L)                  | $\begin{array}{rcl} R1 \ = \ 270 \ \Omega, \\ R2 \ = \ 470 \ \Omega \end{array}$ | 300 pF | S1 Closed <sup>§</sup> |        | · 10 | 18  | ns   |

| t <sub>pd</sub>   | Propagation time, $\overline{DLE}$ low to $\overline{ADx}$ ( $\overline{A}/D = H$ )   | $\begin{array}{rcl} R1 &=& 270 \ \Omega, \\ R2 &=& 470 \ \Omega \end{array}$     | 300 pF | S1 Closed <sup>§</sup> |        | 11   | 18  | ns   |

| t <sub>pd</sub>   | Propagation time, $\overline{A}/D$ to $\overline{AD}x$                                | $\begin{array}{rcl} R1 &=& 270 \ \Omega, \\ R2 &=& 470 \ \Omega \end{array}$     | 300 pF | S1 Closed <sup>§</sup> |        | 10   | 16  | ns   |

| t <sub>pd</sub>   | Propagation time, ACLK to IDEQ                                                        | $R_L = 500 \Omega$                                                               | 50 pF  | 1                      |        | 12   | 20  | ns   |

| tpd               | Propagation time, ACLK to SSEQ                                                        | $R_L = 500 \Omega$                                                               | 50 pF  | ٩                      |        | 12   | 18  | ns   |

| t <sub>pd</sub>   | Propagation time, IDx to IDEQ                                                         | $R_L = 500 \Omega$                                                               | 50 pF  | 1                      |        | 12   | 22  | ns   |

| tpd               | Propagation time, IDx to SSEQ                                                         | $R_L = 500 \Omega$                                                               | 50 pF  | 1                      |        | 12   | 22  | ns   |

| t <sub>en</sub>   | Enable time, AEN to Ax                                                                | $\begin{array}{rcl} R1 &=& 500 \ \Omega, \\ R2 &=& 500 \ \Omega \end{array}$     | 50 pF  | +                      |        | 10   | 16  | ns   |

| t <sub>en</sub>   | Enable time, DEN to Dx                                                                | $R1 = 500 \Omega,$<br>$R2 = 500 \Omega$                                          | 50 pF  | ŧ                      |        | 10   | 16  | ns   |

| t <sub>en</sub>   | Enable time, ADEN to ADx                                                              | $\begin{array}{rcl} R1 &=& 270 \ \Omega, \\ R2 &=& 470 \ \Omega \end{array}$     | 300 pF | ş                      |        | 10   | 18  | ns   |

| tdis              | Disable time, AEN to Ax                                                               | $\begin{array}{rcl} R1 &=& 500 \ \Omega, \\ R2 &=& 500 \ \Omega \end{array}$     | 50 pF  | +                      |        | 6    | 10  | ns   |

| t <sub>dis</sub>  | Disable time, DEN to Dx                                                               | $\begin{array}{rcl} R1 \ = \ 500 \ \Omega, \\ R2 \ = \ 500 \ \Omega \end{array}$ | 50 pF  | +                      |        | 6    | 10  | ns   |

| <sup>t</sup> dis  | Disable time, ADEN to ADx                                                             | R1 = 270 Ω, R2 = 470 Ω                                                           | 50 pF  | ş                      |        | 6    | 10  | ns   |

<sup>†</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. <sup>‡</sup>See Parameter Measurement Information for load circuit (three-state outputs, A15-A0, D15-D0) and voltage waveforms. <sup>§</sup>See Parameter Measurement Information for load circuit (NuBus™ Interface, AD15-AD0) and voltage waveforms.

See Parameter Measurement Information for load circuit (bi-state totem-pole outputs, SSEQ, IDEQ) and voltage waveforms.

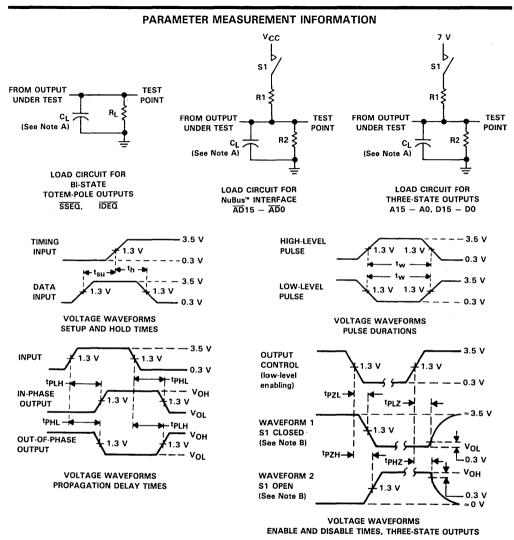

# SN74BCT2420 NuBus™ ADDRESS/DATA TRANSCEIVERS AND REGISTERS

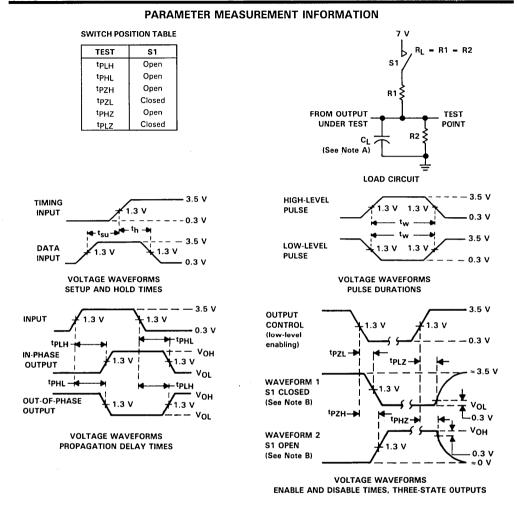

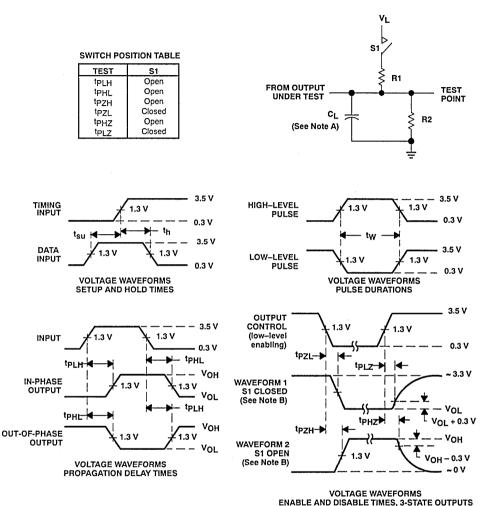

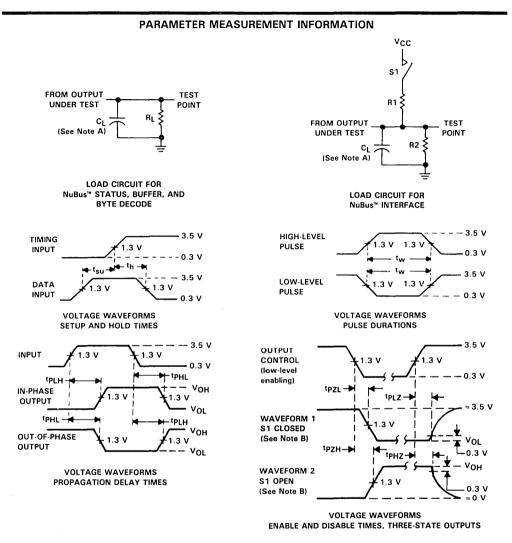

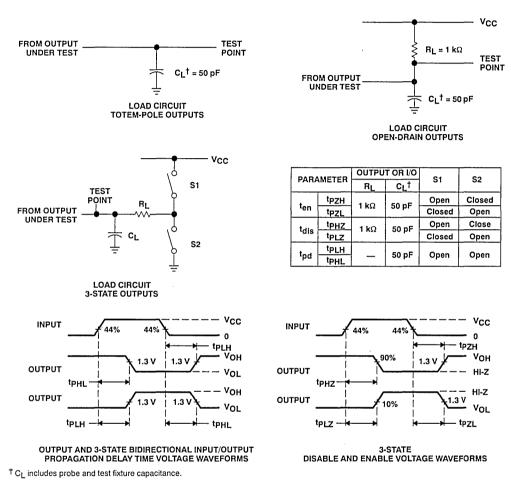

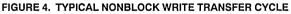

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal condition such that the output is high except when disabled by the output control.

C. All input pulses have the following characteristics: PRR ≤ 1 MHz, t<sub>r</sub> = t<sub>f</sub> = 2 ns, duty cycle = 50%

- D. The outputs are measured one at a time with one transition per measurement.

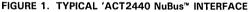

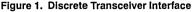

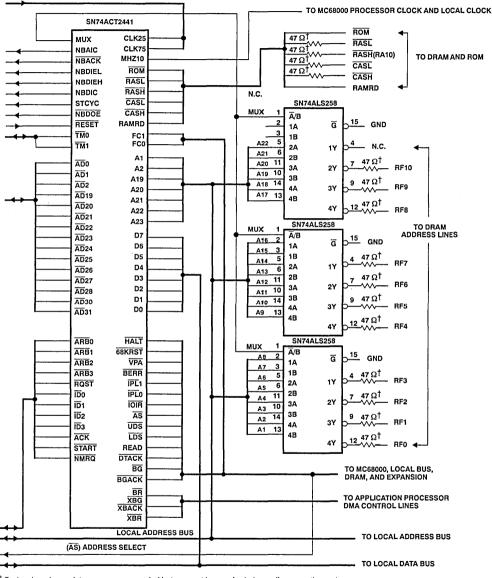

FIGURE 1

# SN74BCT2420 NuBus™ ADDRESS/DATA TRANSCEIVERS AND REGISTERS

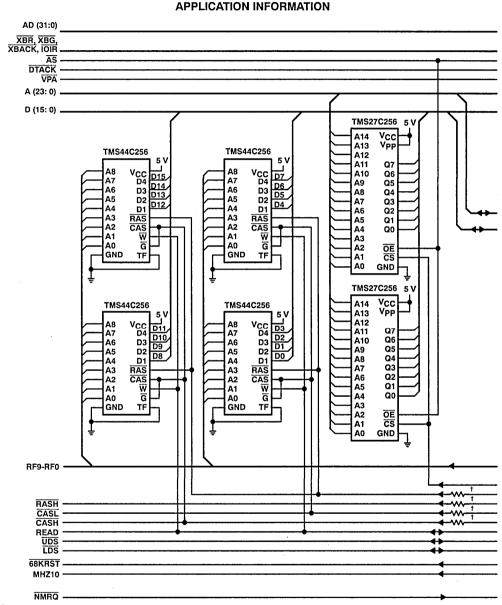

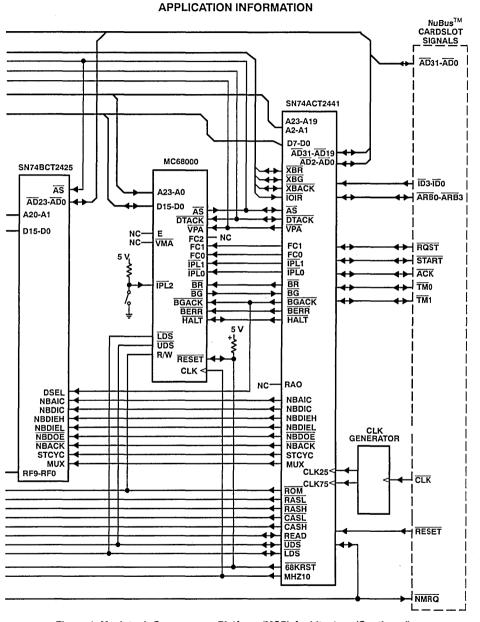

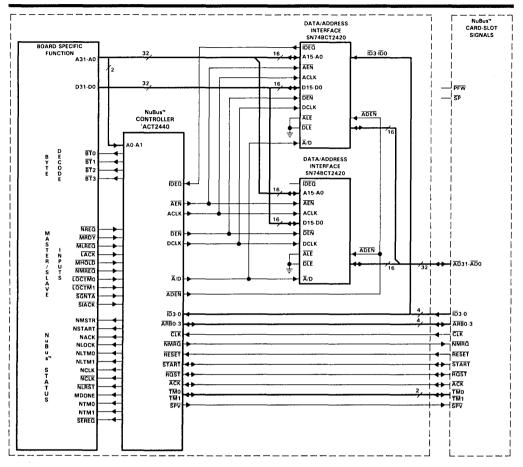

# APPLICATION INFORMATION

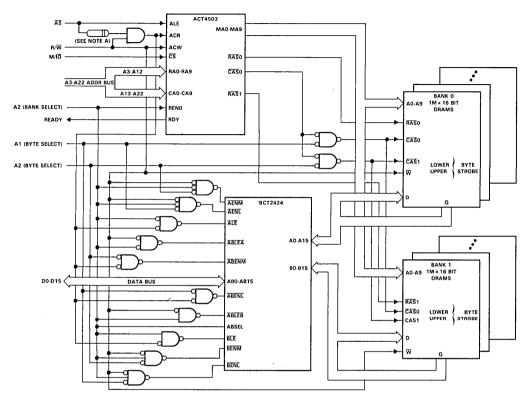

FIGURE 2. TYPICAL NuBus™ INTERFACE

D3305, JULY 1989-REVISED OCTOBER 1989

- Multiplexed Real-Time and Latched Data

- Byte Control for Byte-Write Applications

- Useful in NuBus<sup>™</sup> Interface Applications

- Useful in Memory Interleave Applications

- BiCMOS Design Substantially Reduces

Standby Current

- Dependable Texas Instruments Quality and Reliability

## description

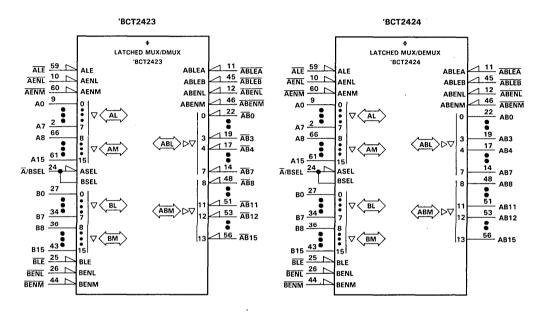

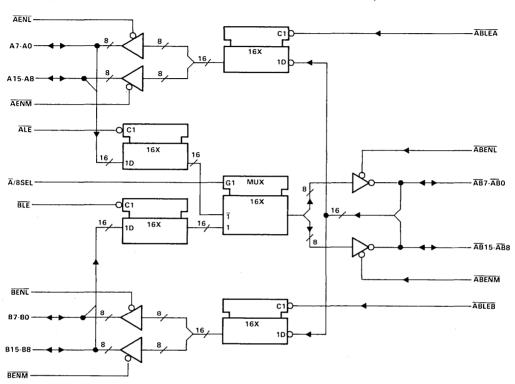

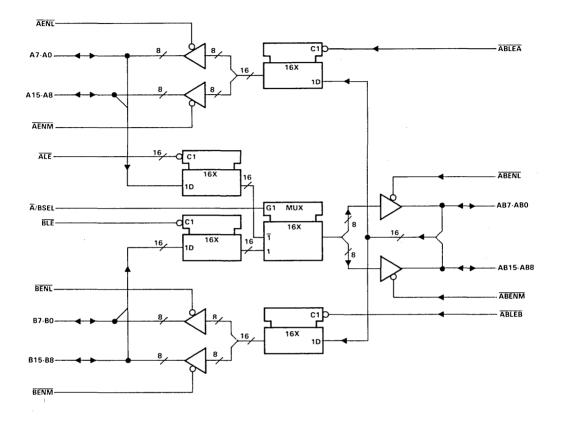

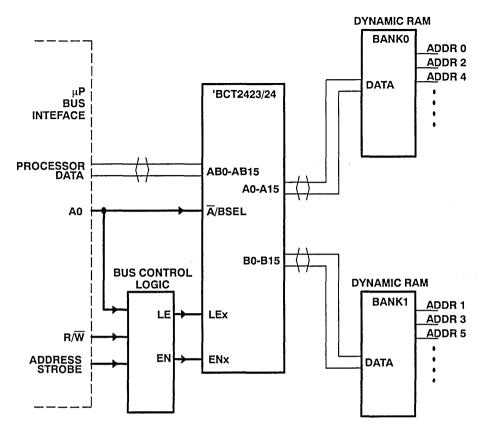

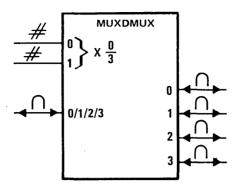

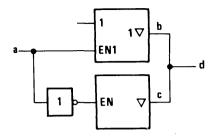

The 'BCT2423 and 'BCT2424 are generalpurpose 16-bit bidirectional transceivers with data storage latches and byte control circuitry arranged for use in applications where two separate data paths must be multiplexed onto, or demultiplexed from, a single data path. Typical applications include multiplexing and/or demultiplexing of address and data information in microprocessor- or bus-interface applications. These devices are also useful in memoryinterleaving applications. The 'BCT2423 and 'BCT2424 offer inverted and noninverted data paths, respectively.

The 'BCT2423 and 'BCT2424 were designed using Texas Instruments BiCMOS process, which features bipolar drive characteristics, but also greatly reduces the standby power of the device when disabled. This is valuable when the device is not performing an address or data transfer.

Three 16-bit I/O ports, A15-AO, B15-BO, and AB15-ABO are available for address and/or data transfer. The <u>AENM</u>, <u>AENL</u>, <u>BENM</u>, <u>BENL</u>, <u>ABENM</u>, and <u>ABENL</u> inputs control the bus transceiver functions. These control signals also allow byte-control of the most significant byte and least significant byte for each bus.

Address and/or data information can be stored using the internal storage latches. The  $\overline{ALE}$ ,  $\overline{BLE}$ ,  $\overline{ABLEA}$ , and  $\overline{ABLEB}$  inputs are active low, and are used to control data storage. When the latch enable input is low, the latch is transparent. When the latch enable input goes high, the data present at the inputs is latched, and remains latched until the latch enable input is returned low.

NuBus is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

## description (continued)

Data on the 'A' bus and 'B' bus are multiplexed onto the 'AB' bus via the  $\overline{A}$ /BSEL control line. When  $\overline{A}$ /BSEL is low, A15-A0 is mapped to the AB15-AB0 outputs. When  $\overline{A}$ /BSEL is high, B15-B0 is mapped to the AB15-AB0 outputs.

The SN74BCT2423 and SN74BCT2424 are characterized for operation from 0 °C to 70 °C.

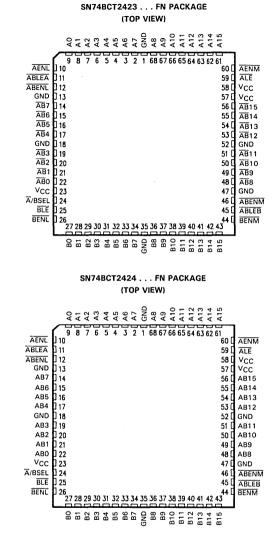

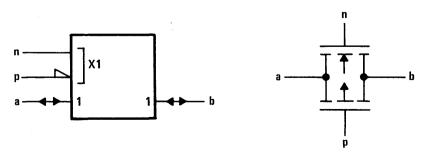

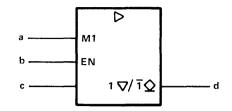

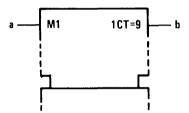

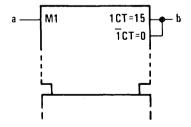

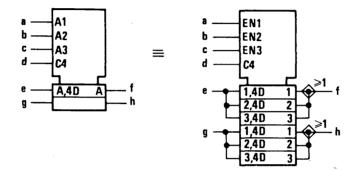

### logic symbols<sup>†</sup>

<sup>†</sup>These logic symbols are in accordance with ANSI/IEEE Std 91-1984.

,

logic diagram (positive logic)

logic diagram (positive logic)

## **TERMINAL FUNCTIONS**

| PIN NAME   | DESCRIPTION                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| A15-A0     | A Bus. This 16-bit I/O port allows for transmission of data and/or address information to or from the AB bus. Information |

|            | transfer between the A bus and the AB bus is inverting for the 'BCT2423 and noninverting for the 'BCT2424.                |

| AB15-AB0   | AB Bus. This 16-bit I/O port allows for multiplexed transmission of data and/or address information to or from the        |

| ('BCT2423) | A and B buses. Information transfer between the A, B and AB buses is inverting for the 'BCT2423 and noninverting          |

| AB15-AB0   | for the 'BCT2424.                                                                                                         |

| ('BCT2424) |                                                                                                                           |

| ABENL      | AB Bus Output Enable, Least Significant Byte. This active-low input is used to enable the AB7-AB0 outputs. When           |

|            | this input is high, the AB7-AB0 outputs are in the high-impedance state allowing for data input.                          |

| ABENM      | AB Bus Output Enable, Most Significant Byte. This active-low input is used to enable the AB15-AB8 outputs. When           |

|            | this input is high, the AB15-AB8 outputs are in the high-impedance state allowing for data input.                         |

| ABLEA      | AB Bus Latch Enable to A Bus. This active-low input is used to control the latch that holds data received from the        |

|            | AB bus (AB15-AB0) to be transferred to the A bus (A15-A0). When ABLEA is low, the latch is transparent. When              |

|            | ABLEA transitions to the high level, the data present at the AB15-ABO inputs is latched, and remains latched while        |

|            | ABLEA is high.                                                                                                            |

| ABLEB      | AB Bus Latch Enable to B Bus. This active-low input is used to control the latch that holds data received from the        |

|            | AB bus (AB15-AB0) to be transferred to the B bus (B15-B0). When $\overline{ABLEB}$ is low, the latch is transparent. When |

|            | ABLEB transitions to the high level, the data present at the AB15-ABO inputs is latched, and remains latched while        |

|            | ABLEB is high.                                                                                                            |

| Ā/BSEL     | A/B Select Control. This input controls the A/B multiplexer. When the input is low, A15-A0 is selected as input to        |

|            | the AB15-AB0 outputs. When the input is high, B15-B0 is selected as input to the AB15-AB0 outputs.                        |

| AENL       | A Bus Output Enable, Least Significant Byte. This active-low input is used to enable the A7-A0 outputs. When this         |

|            | input is high, the A7-A0 outputs are in the high-impedance state allowing for data input.                                 |

| AENM       | A Bus Output Enable, Most Significant Byte. This active-low input is used to enable the A15-A8 outputs. When this         |

|            | input is high, the A15-A8 outputs are in the high-impedance state allowing for data input.                                |

| ALE        | A Bus Latch Enable. This active-low input is used to control the latch that holds data received from the A bus (A15-A0).  |

|            | When ALE is low, the latch is transparent. When ALE transitions to the high level, the data present at the A15-A0         |

|            | inputs is latched and remains latched while ALE is high.                                                                  |

| B15-B0     | B Bus. This 16-bit I/O port allows for transmission of data and/or address information to or from the AB bus. Information |

|            | transfer between the B bus and the AB bus is inverting for the 'BCT2423 and noninverting for the 'BCT2424.                |

| BENL       | B Bus Output Enable, Least Significant Byte. This active-low input is used to enable the B7-B0 outputs. When this         |

|            | input is high, B7-B0 outputs are in the high-impedance state allowing for data input.                                     |

| BENM       | B Bus Output Enable, Most Significant Byte. This active-low input is used to enable the B15-B8 outputs. When this         |

|            | input is high, the B15-B8 outputs are in the high-impedance state allowing for data input.                                |

| BLE        | B Bus Latch Enable. This active-low input is used to control the latch that holds data received from the B bus (B15-B0).  |

|            | When BLE is low, the latch is transparent. When BLE transitions to the high level, the data present at the B15-B0         |

|            | inputs is latched and remains latched while BLE is high.                                                                  |

|                 | DIRECTION A OR B TO AB |     |     |        |        |              |           |                |        |        |  |  |  |

|-----------------|------------------------|-----|-----|--------|--------|--------------|-----------|----------------|--------|--------|--|--|--|

|                 | INPUTS OUTPUTS         |     |     |        |        |              |           |                |        |        |  |  |  |

| INPUTS          |                        |     |     |        |        |              |           | 2423           | 'BCT   | 2424   |  |  |  |

| Ax              | Bx                     | ALE | BLE | A/BSEL | AB15-8 | <b>AB7-0</b> | AB15-8    | AB7-0          |        |        |  |  |  |

| Н               | HXLXLLL L H            |     |     |        |        |              |           |                |        |        |  |  |  |

| L X L X L L L Н |                        |     |     |        |        |              |           |                | L L    |        |  |  |  |

| х               | х                      | н   | х   | L      | L      | L            | AE        | Īo             | AE     | 30     |  |  |  |

| х               | н                      | Х   | L   | н      | L      | L            | L         |                | ŀ      | 1      |  |  |  |

| х               | ٤                      | х   | L   | н      | L      | L            | F         | 1              | L      |        |  |  |  |

| х               | х                      | х   | н   | н      | L      | L            | AE        | <sup>B</sup> o | AE     | 30     |  |  |  |

| х               | х                      | х   | х   | х      | L      | L            | Active    | Active         | Active | Active |  |  |  |

| х               | х                      | х   | х   | х      | L      | н            | Active Z  |                | Active | z      |  |  |  |

| х               | х                      | х   | х   | х      | н      | L            | Z Active  |                | z      | Active |  |  |  |

| х               | х                      | х   | х   | х      | н      | н            | z z z z z |                |        |        |  |  |  |

FUNCTION TABLES

|     | DIRECTION AB TO A OR B |        |                   |                   |                |        |                |        |  |  |  |  |  |

|-----|------------------------|--------|-------------------|-------------------|----------------|--------|----------------|--------|--|--|--|--|--|

|     |                        | INPUTS |                   |                   |                | OUT    | PUTS           |        |  |  |  |  |  |

| ABx | ABLEA                  | ABLEB  | AENL <sup>†</sup> | BENL <sup>†</sup> | 'BCT           | 2423   | 'BCT2424       |        |  |  |  |  |  |

| ABx | ADLEA                  | ADLED  | AENM <sup>†</sup> | BENM <sup>†</sup> | Ах             | Bx     | Ax             | Bx     |  |  |  |  |  |

| н   | L                      | L      | L                 | L                 | L              | L      | н              | н      |  |  |  |  |  |

| L   | L                      | L      | L                 | L                 | н              | н      | L              | L      |  |  |  |  |  |

| н   | L                      | н      | L                 | L                 | L              | BO     | н              | BO     |  |  |  |  |  |

| L   | L                      | н      | L                 | L                 | н              | BO     | L              | BO     |  |  |  |  |  |

| н   | н                      | Ĺ      | L                 | L                 | A <sub>0</sub> | L      | AO             | н      |  |  |  |  |  |

| L   | н                      | L      | L                 | L                 | AO             | н      | AO             | L      |  |  |  |  |  |

| ×   | H                      | н.     | L                 | L                 | AO             | BO     | A <sub>0</sub> | BO     |  |  |  |  |  |

| х   | х                      | Х      | L                 | L                 | Active         | Active | Active         | Active |  |  |  |  |  |

| X   | х                      | х      | L                 | н                 | Active         | Z      | Active         | Z      |  |  |  |  |  |

| X   | х                      | х      | н                 | L                 | z              | Active | z              | Active |  |  |  |  |  |

| X   | х                      | х      | н                 | н                 | z              | Z      | Z              | Z      |  |  |  |  |  |

H = high level, L = low level, X = irrelevant, Z = high impedence,

$A_0$ ,  $B_0$ ,  $AB_0$ ,  $AB_0$  = no change since the controlling latch enable went high

<sup>1</sup> The least significant bytes (A7-A0 and B7-B0) and the most significant bytes (A15-A8 and B15-B8) can be independently enabled and disabled, as was illustrated for the AB and AB bytes in the upper function table.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, VCC (see Note 1)               |  |

|------------------------------------------------|--|

| Input voltage (all inputs and I/O ports) 5.5 V |  |

| Operating free-air temperature range           |  |

| Storage temperature range                      |  |

<sup>†</sup>Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "recommended operating conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

## recommended operating conditions

|                 | PARAM                         |                          | SN   | 74BCT2 | 423  | SN   | 74BCT2 | 424  | UNIT |  |

|-----------------|-------------------------------|--------------------------|------|--------|------|------|--------|------|------|--|

| 1               | PARAM                         | EIER                     | MIN  | NOM    | МАХ  | MIN  | NOM    | MAX  | UNIT |  |

| Vcc             | Supply voltage                |                          | 4.5  | 5      | 5.5  | 4.5  | 5      | 5.5  | V    |  |

| VIH             | High-level input voltage      |                          | 2    |        |      | 2    |        |      | V    |  |

| VIL             | Low-level input voltage       |                          |      | 0.8    |      |      | 0.8    | v    |      |  |

|                 |                               | Ax, Bx outputs           |      |        | - 15 |      |        | -15  |      |  |

| юн              | High-level output current     | ABx or ABx outputs       |      |        | - 15 |      |        | - 15 | mA   |  |

|                 |                               | Ax, Bx outputs           |      |        | 24   |      |        | 24   |      |  |

| <sup>I</sup> OL | Low-level output current      | ABx or ABx outputs       |      |        | 48   |      |        | 48   | mA   |  |

|                 | Dulas duration                | ABLEA, ABLEB high or low | 12.5 |        |      | 12.5 |        |      |      |  |

| tw              | Pulse duration                | ALE, BLE high or low     | 12.5 |        |      | 12.5 |        |      | ns   |  |

| t <sub>su</sub> | Setup time                    | Data before xLEx 1       | 10   |        |      | 10   |        |      | ns   |  |